この記事はオープンソース半導体 Advent Calendar 2025の13日目の記事です。

先日参加した、ISHI会主催の2025年09月イベント:二日でOPAMP回路ハンズオンでオペアンプ半導体を設計したときに得た知見をここに記録していきます。

このイベントでは、半導体としてのアナログ回路設計について、二段差動増幅オペアンプを通して学びました。2日間のハンズオンとその後の1週間の宿題期間で作成したレイアウトは、相乗りチップとして製造予定です。相乗りチップとは、1つの半導体チップのスペースやピンを複数人で共有し、1人あたりの製作費用を抑える試みです。詳細はイベントページやISHI会のホームページを参照してください。

イベントの参加ページには以下のような脅し文句注意書きがありました。

- 【チップ製造(あり)枠参加資格】(なし枠での条件は「2」と「3」のみとなります)

- 2日連続で10-18時で参加できる方

- オープンソース半導体のEDAツールの使い方は理解している方

- テスト運用と理解して参加してもらえる方

- レイアウトは自宅で一週間以内に完成されられる方

!!!特大注意!!!テスト運用ということもあり、スパルタハンズオンとなります。ついていけないと判断した人は、容赦なく切り捨てていきます。理由は、「どのレベルくらいの方」が「どのくらいのレベルの解説をすると付いてこれなくなるのか?」を探るためのテスト運用となるためです。その条件であると理解して参加してください。

自分は回路シミュレータのxschemや半導体レイアウトソフトのklayoutを使うのも初めてだったので戦々恐々としていましたが、事前に予習して臨むことでなんとかなりました(と個人的には思っています)。その1週前にはインバータ設計ハンズオンが開催されており、その資料が学習用に公開されていたこともありがたかったです。

このオペアンプ回路ハンズオンは、電気系ものづくりYoutuberのイチケンさんが体験されたのと同じカリキュラムで運営されていたようです。気になる方はそちらの体験記も参照してください。

ハンズオンでは

- 理論の説明

xschemによる回路シミュレーション・パラメータ決定klayoutによる回路レイアウト

を実施しましたが、1と2の「理論編」は説明資料を参照していただくことにして、本記事では3の「レイアウト編」をメインに、私が体験したこと・得られた知見を書いていきます。

理論編

ハンズオンで使用した説明資料はISHI会のリポジトリで公開されているので、そちらを参照してください。本記事中でも、『OPAMP設計(TR10)』という資料の内容を引用します。

xschemを使用した回路シミュレーションでは、オペアンプ全体や内部で使用するトランジスタについて、以下の性質を調べていきます。

- Vgs–Idカーブ

- 飽和領域

- 相互コンダクタンス

- 出力抵抗

- 短チャネル効果

- オーバードライブ電圧

- Ibias(バイアス電流)

- 増幅率

- オープンループ特性

- スルーレート

- CMRR

- PSRR

- 温度解析

色々とやっていますが、ここで決定したいのはトランジスタのゲート長Lとゲート幅Wです。今回は利得の大きさ(Lを大きくしたい)と高周波性能(Lを小さくしたい)のバランスをとってL=3umとしました。トランジスタに流れる電流はW/L比によって決まるので、各パーツの要求に合わせて30um単位で変化させました。

ここで、反省というか注意があります!これまでの説明や資料では、回路シミュレーションを通して最適なL, Wを決定しているように見えますが、実際はレイアウト制限を重視して決めた方がいいです。

ゲート長Lとゲート幅Wはその名のとおりレイアウトの大きさに直結してくるため、無制限に増やせるわけではありません。私は(持ち前の運の良さから)奇跡的にレイアウトに収まるW, Lを得ることができましたが、実際はレイアウト制限からW, Lを決定し、上記の項目が許容できる範囲かチェックするという、妥協を積み上げて実装するのがよいと思います。

レイアウト編

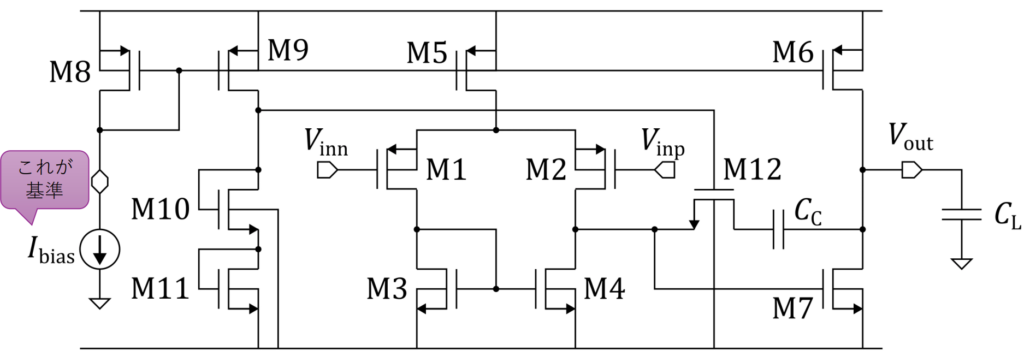

各種パラメータを決定したら、klayoutを使って指定されたサイズ内でパーツを配置・配線していきます。実装する回路は図1のとおりです(『OPAMP設計(TR10)』より引用)。つまり、図2のVoutよりも左側にある12個のトランジスタと1個のキャパシタを配置する必要があります。

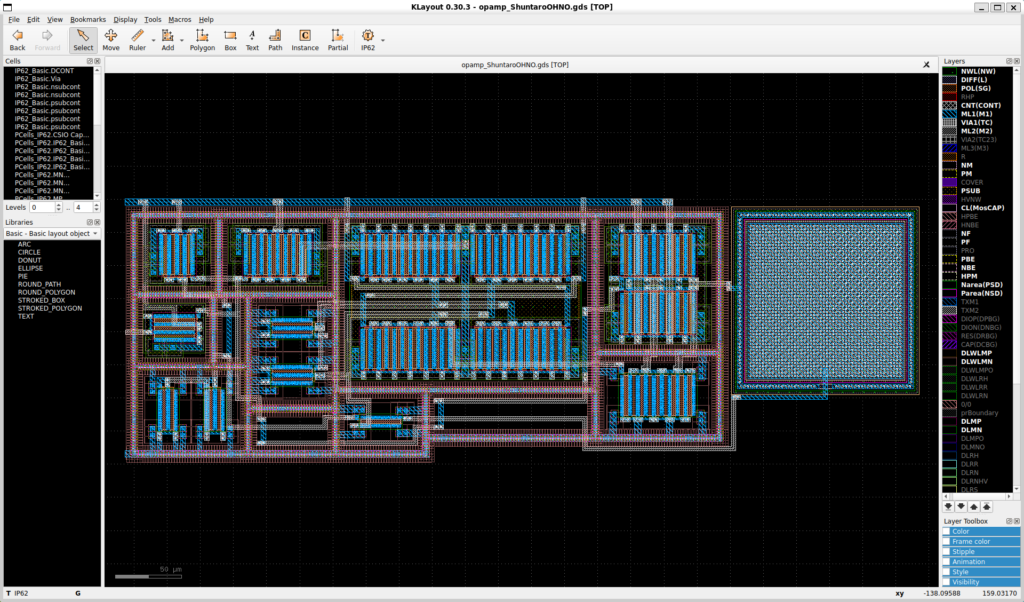

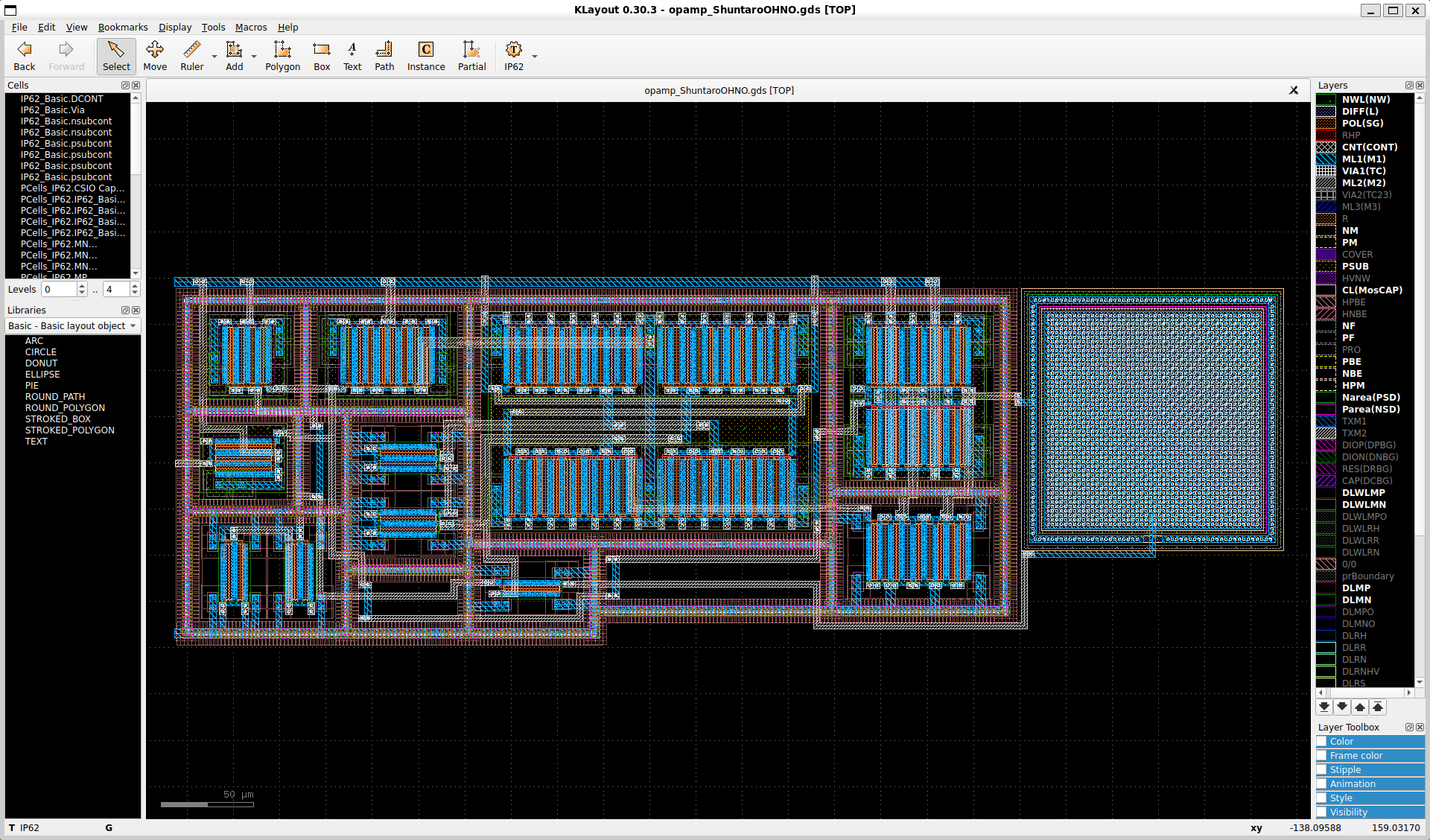

今回は最大で600um×200umに収めるように指定されていました。完成したレイアウトは以下のとおりで、ギリギリ範囲内に収めることができました。

このレイアウトを振り返りながら、得られた知見や注意点をいくつか共有します。

キャパシタがデカすぎるッピ!

図2のレイアウトの右端に鎮座している、謎の正方形を見てください。これは位相補償用のキャパシタ(コンデンサ)です。図1ではCCという名前が付けられています。

このキャパシタを挟むことで、高周波領域での位相のずれを軽減することができます。図2では設置できる最大サイズのものを配置していますが、これでも容量は8.856pFしかありません。性能上は最低限の大きさなので、これより小さくすることは難しいです。よって、600um×200umのレイアウト領域から、いきなり約150um×150umが持って行かれます。所得税か?

また、後述するガードリングの幅を考慮すると、200umから150umを引いた残りの50umにはトランジスタを配置するのは困難です。よって、実質450um×200umの中に12個のトランジスタを収納する必要があります。

ガードリングと配線

VSSに接続されるpsubcont(図2ではピンク色に見える)でトランジスタを囲うことで、ノイズを削減することができます。これをガードリングといいます。

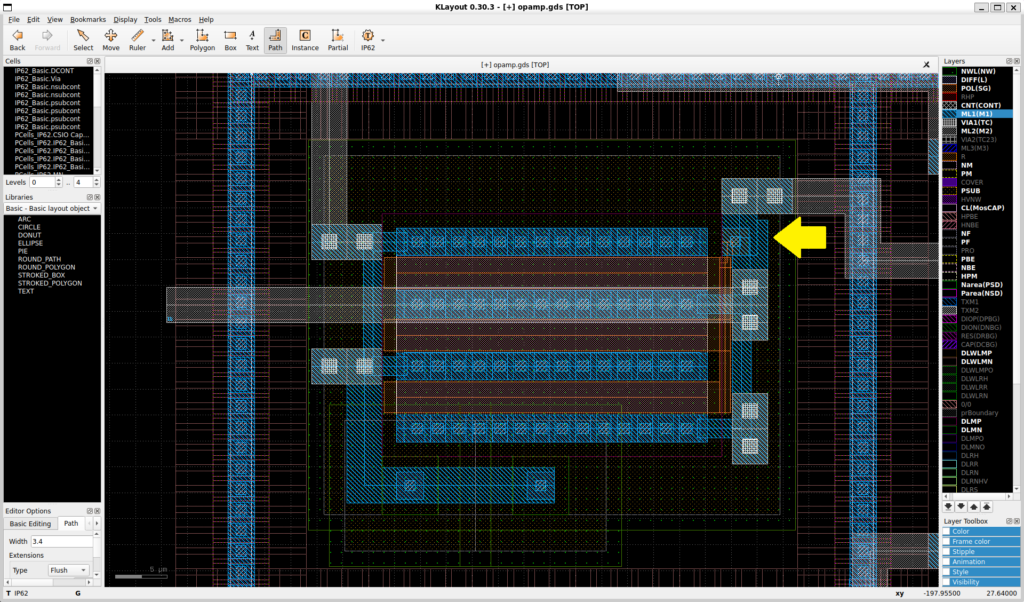

ガードリングでトランジスタを囲った場合、パーツ間を接続するために、配線でガードリングを乗り越える必要があります。レイアウトの配線にはメタル第1層(青)と第2層(白)が使え、メタル第1層をVSSに接続する設定のときは、メタル第2層を使ってガードリングを乗り越えます。

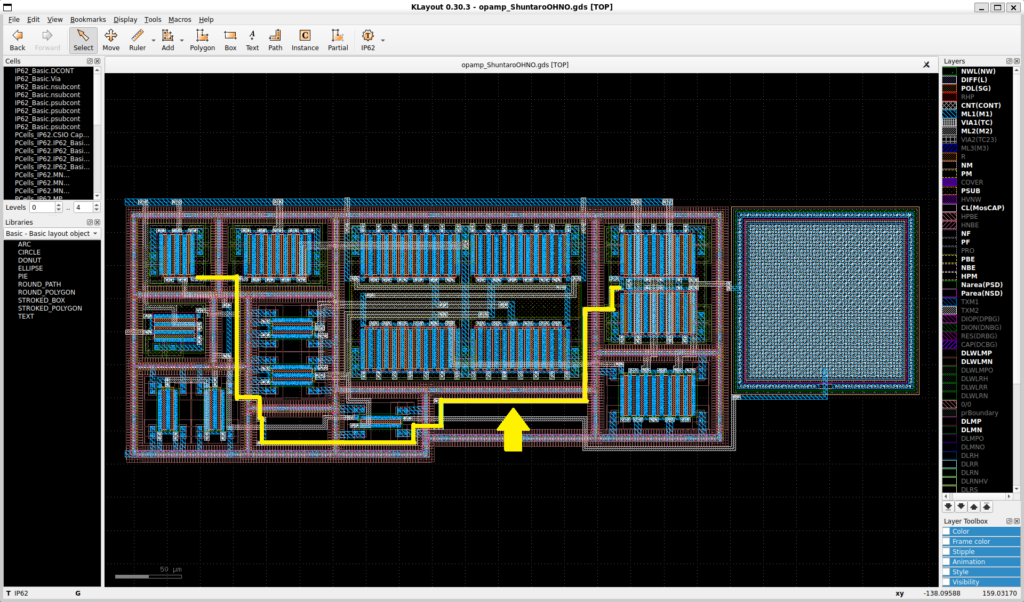

メタル第1層と第2層を使うことで、配線を交差することもできます。その結果、今回は交差を繰り返して、図3のような非常に長い配線も出てきてしまいました(図1のM5, 8, 9とM6を接続する配線です)。パズル的な側面もありますが、全体で配線長を揃えた方がバランス的にも性能的にも良かったかもしれません。

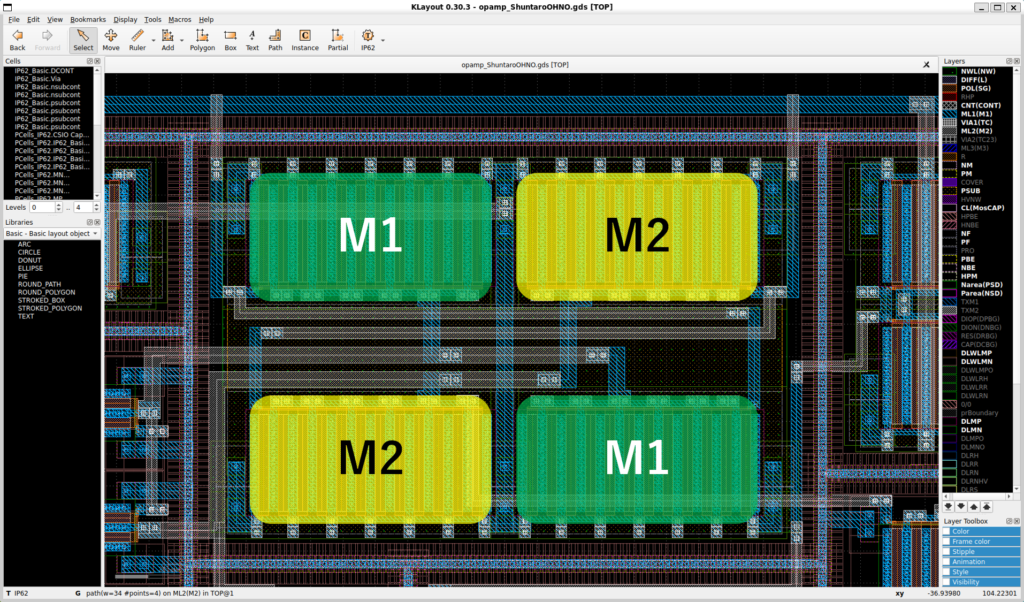

コモンセントロイド(トランジスタの数を間違えない)

大電流が流れるトランジスタの性能を安定させるためには、温度の管理が重要になります。図1のM1とM2のように、対として動作するトランジスタの場合、これらの特性が温度によって変化しても、それぞれの変化幅が一定であれば全体としては正常に機能します。これを実現するのが、図4に示すコモンセントロイドというレイアウトです。それぞれのトランジスタを偶数個に分解し、それぞれが対象になるように配置します。このようにすると、トランジスタの上下左右のいずれかに熱源が偏っていた場合でも、M1とM2の温度勾配が等しくなります。

このテクニックは可能な限り実施した方が良いのですが、やってみて感じたデメリットはトランジスタの数を数えにくくなることです。ぱっと見で4個のトランジスタがあるため、M1~4を配置し終えたと錯覚し、まだ余裕があると見積もっていたレイアウト領域が本当にギリギリだったというスリリングな体験をしました。

DRCとLVSチェック

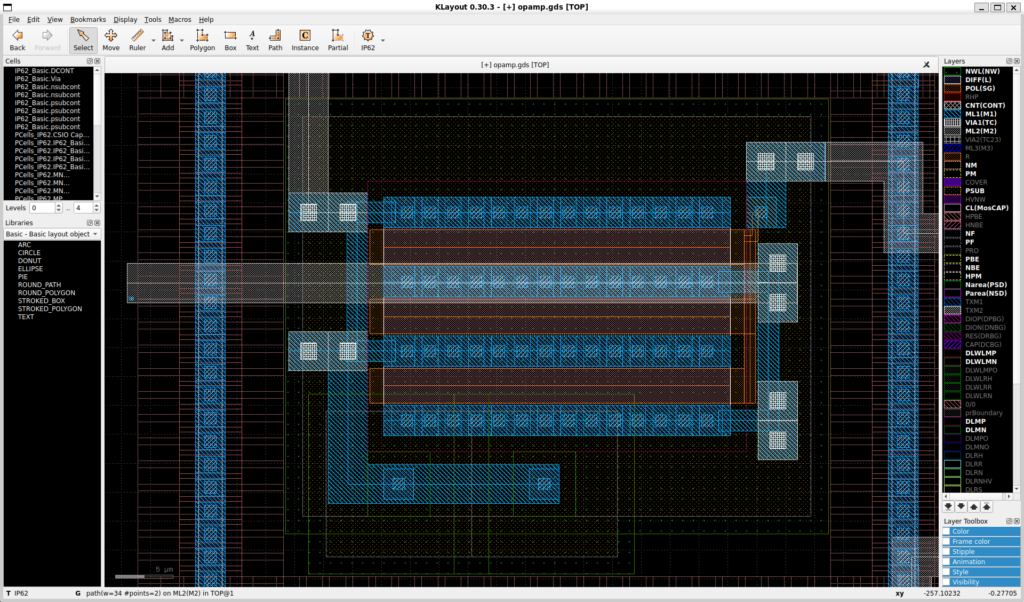

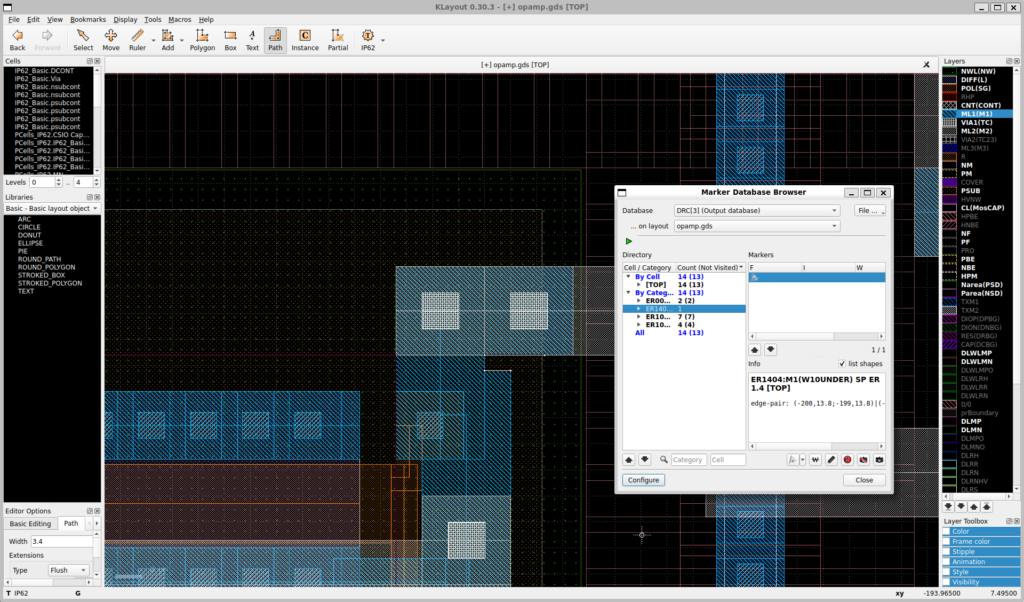

レイアウトが正しく完了したことを確認するために、DRCとLVSという2つのチェックを実施します。DRC(Design Rule Checking)は、配線間に必要な最小間隔など、製造装置の制約から決まるレイアウトルールが満たされているかを確認します。

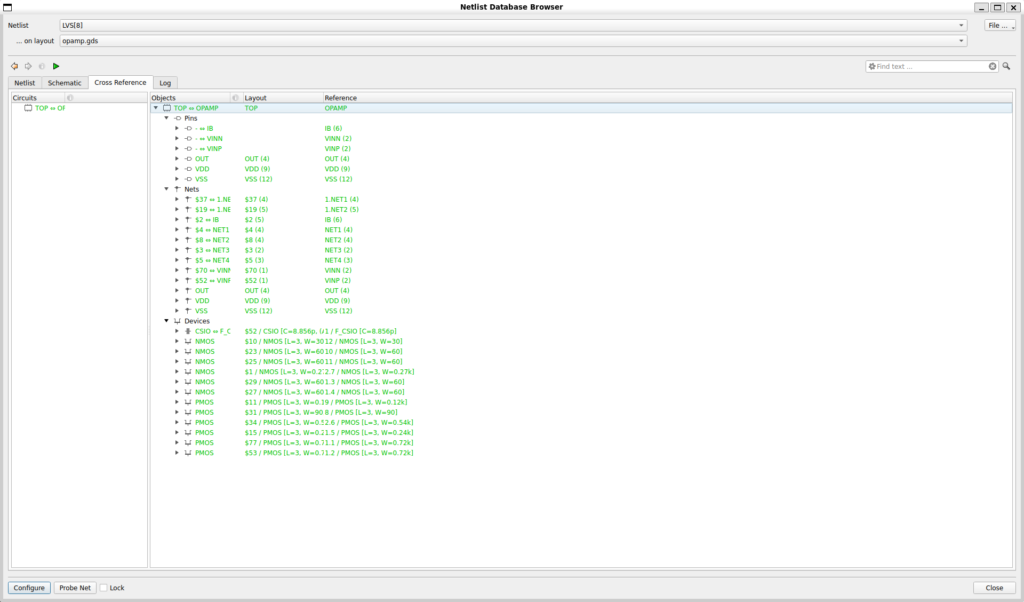

図5はDRCチェックが完了した後の、図1でいうM8付近の拡大図です。この状態で、引き続きLVS(Layout Versus Schematic)を検証します。ここでは、作成したレイアウトと回路図が一致しているかをチェックします。

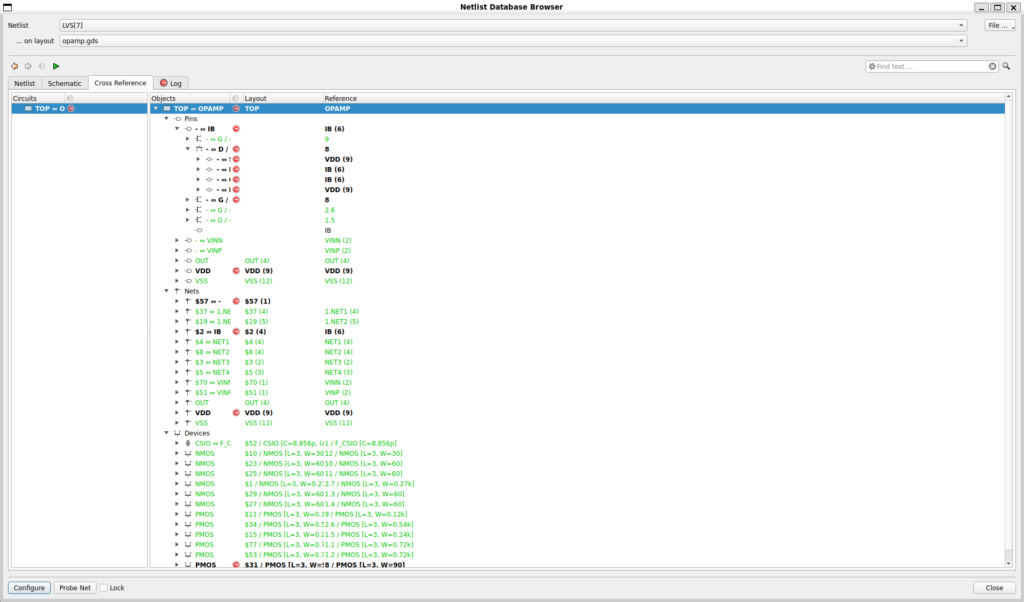

その結果、エラーが出てしまいました(図6)。どうやら、M8のD(ドレイン)とG(ゲート)が接続されていないことが問題のようです。

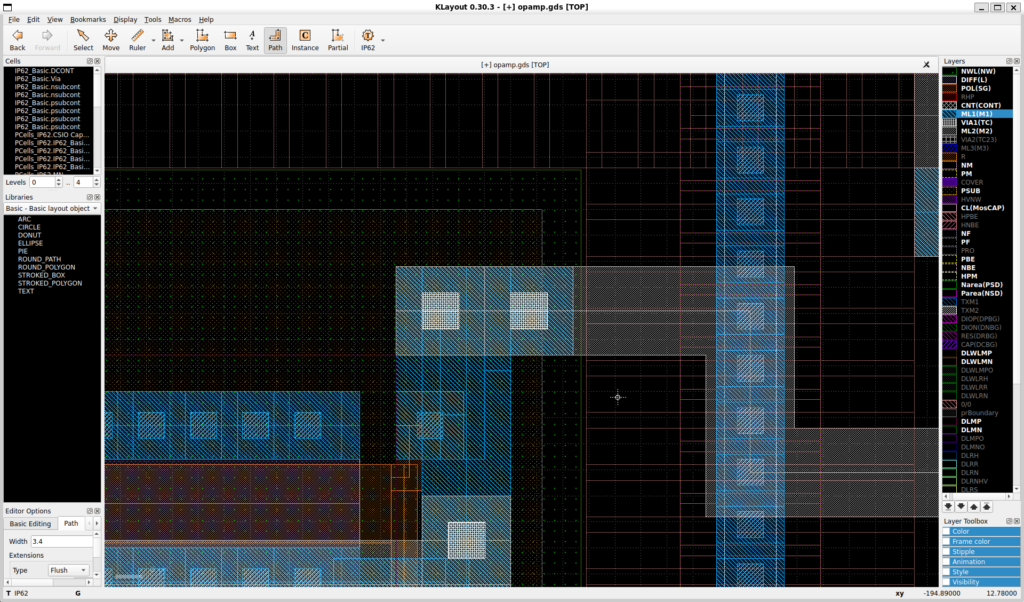

これを図7のようにチョチョイと修正しました。この状態で再度LVSを実行します。

すると、図8のようにレイアウトと回路図が完全に一致したことを確認できました。これで作業完了!と思って意気揚々と提出したのですが…

よく確認すると、新規に追加した配線によってDRCエラーが出現していました。このように、DRCとLVSは独立しているため、両方が確実に通ったことを確かめる必要があります。その節はご迷惑をおかけしました。

最後に

以上、色々とつまづきポイントがありましたが、なんとかレイアウトを提出することができました。しばらくすると、この回路が搭載されたチップが送られてくるはずなので、想定した性能が出ているか検証したいと思います。ドキドキワクワクの瞬間です。

今回のハンズオンは、資料がしっかりしていたため、指示通りに手を動かすことで最後まで行けました。ただ、半導体やオペアンプの理論に関して理解が不十分な部分も多いので、引き続き勉強が必要だと痛感しました。

コメント